Configware/Software-Co-Compilation

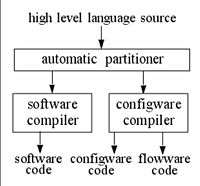

Software/Configware Co-Compilation is used for reconfigurable computing to generate the code for both, an instruction-stream-based microprocessor and a reconfigurable accelerator interfaced to it. Such a co-compiler (see figure) has a partitioner which accepts input from a high level language source, such as, for instance a programming language, or the output from tools like MATLAB, and automatically partitions it into parallelizable parts suitable for the reconfigurable accelerator and the rest for running on the microprocessor. By loop transformations the partitioner converts the parallelizable parts into a configware source, which is compiled by a Configware Compiler generating configware code for the configuration of the reconfigurable accelerator like, for instance an FPGA, or a coarse-grained reconfigurable array, and flowware code for organizing the data streams going from and to the accelerator.

Further reading

- 1995 J. Becker, et al.: A Novel Two-Level Hardware/Software Co-Design Framework; Journal of the Brazilian Computer Society, Special Issue on Electronic Design Automation, Dec. 1995

- 1995 J. Becker, et al.: A Profiling-driven Hardware/Software Partitioning of High-Level Language Specifications; Workshop on Logic and Architecture Synthesis, Grenoble, France, Dec. 1995

- 1996 J. Becker, et al.: CoDe-X: A Novel Two-Level Hardware/Software Co-Design Framework; 9th International Conference on VLSI Design, Bangalore, India, Jan. 1996