List of integrated circuit packaging types

Integrated circuits are put into protective packages to allow easy handling and assembly onto printed circuit boards and to protect the devices from damage. A very large number of different types of package exist. Some package types have standardized dimensions and tolerances, and are registered with trade industry associations such as JEDEC and Pro Electron. Other types are proprietary designations that may be made by only one or two manufacturers. Integrated circuit packaging is the last assembly process before testing and shipping devices to customers.

Occasionally specially-processed integrated circuit dies are prepared for direct connections to a substrate without an intermediate header or carrier. In flip chip systems the IC is connected by solder bumps to a substrate. In beam-lead technology, the metallized pads that would be used for wire bonding connections in a conventional chip are thickened and extended to allow external connections to the circuit. Assemblies using "bare" chips have additional packaging or filling with epoxy to protect the devices from moisture.

Through-hole packages

Through hole technology uses holes drilled through the PCB for mounting the components. The component has leads that are soldered to pads on the PCB to electrically and mechanically connect them to the PCB.

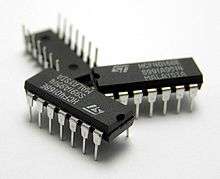

Three 14-pin (DIP14) plastic dual in-line packages containing IC chips.

| Acronym | Full name | Remark |

| SIP | Single in-line package | |

| DIP | Dual in-line package | 0.1 in (2.5 mm) pin spacing, rows 0.3 in (7.6 mm) or 0.6 in (15 mm) apart. |

| CDIP | Ceramic DIP[1]] | |

| CERDIP | Glass sealed ceramic DIP[1] | |

| QIP | Quadruple in-line package | Like DIP but with staggered (zig-zag) pins.[1] |

| SDIP | Skinny DIP | Standard DIP with 0.1 in pin spacing, rows 0.3 in apart.[1] |

| ZIP | Zig-zag in-line package | |

| MDIP | Molded DIP.[2] | |

| PDIP | Plastic DIP.[1] | |

Surface mount

| Acronym | Full name | Remark |

| CCGA | Ceramic Column Grid Array (CGA)[3] | |

| CGA | Column Grid Array[3] | Example |

| CERPACK | Ceramic package [4] | |

| CQGP[5] | | |

| LLP | Lead-Less lead-frame Package | A package with metric pin distribution (0.5–0.8 mm pitch)[6] |

| LGA | Land Grid Array[3] | |

| LTCC | Low temperature co-fired ceramic[7] | |

| MCM | Multi-Chip Module[8] | |

| MICRO SMDXT | Micro Surface Mount Device extended technology[9] | Example |

Chip carrier

A chip carrier is a rectangular package with contacts on all four edges. Leaded chip carriers have metal leads wrapped around the edge of the package, in the shape of a letter J. Leadless chip carriers have metal pads on the edges. Chip carrier packages may be made of ceramic or plastic and are usually secured to a printed circuit board by soldering, though sockets can be used for testing.

| Acronym | Full name | Remark |

| BCC | Bump Chip Carrier [3] | - |

| CLCC | Ceramic Leadless Chip Carrier [1] | - |

| LCC | Leadless Chip Carrier [3] | Contacts are recessed vertically. |

| LCC | Leaded Chip Carrier [3] | - |

| LCCC | Leaded Ceramic Chip Carrier [3] | - |

| DLCC | Dual Lead-Less Chip Carrier (Ceramic) [3] | - |

| PLCC | Plastic Leaded Chip Carrier [1][3] |

- |

Pin grid arrays

| Acronym | Full name | Remark |

| OPGA | Organic Pin Grid Array | - |

| FCPGA | Flip-chip Pin Grid Array [3] | - |

| PAC | Pin Array Cartridge [10] | - |

| PGA | Pin grid array | also known as PPGA [1] |

| CPGA | Ceramic Pin Grid Array [3] | - |

Flat packages

| Acronym | Full name | Remark |

| - | Flatpack | Earliest version metal/ceramic packaging with flat leads |

| CFP | Ceramic Flat Pack [3] | - |

| CQFP | Ceramic Quad Flat-Pack, similar to PQFP [1][3] | - |

| BQFP | Bumpered Quad Flat Pack [3] | - |

| DFN | Dual Flat Pack | No Lead [3] |

| ETQFP | Exposed Thin Quad Flat Package [11] | - |

| PQFN | Power Quad Flat-Pack | No-leads, with exposed die-pad[s] for heatsinking [12] |

| PQFP | Plastic Quad Flat Package [1][3] | - |

| LQFP | Low-profile Quad Flat Package [3] | - |

| QFN | Quad Flat No Leads | Also called as micro lead frame (MLF).[3][13] |

| QFP | Quad Flat Package [1][3] | - |

| MQFP | Metric Quad Flat Pack | QFP with metric pin distribution [3] |

| HVQFN | Heat-sink Very-thin Quad Flat-pack No-leads | - |

| SIDEBRAZE [14][15] | - | - |

| TQFP | Thin Quad Flat Pack [1][3] | - |

| TQFN | Thin Quad Flat No-Lead | - |

| VQFP | Very-thin Quad Flat Pack [3] | - |

| ODFN | Optical Dual Flat No-Lead | IC packaged in transparent packaging used in optical sensor |

Small outline packages

| Acronym | Full name | Remark |

| SOP | Small Outline Package [1] | - |

| CSOP | Ceramic Small Outline Package | - |

| MSOP | Mini Small-Outline Package | - |

| PSOP | Plastic Small-Outline Package [3] | - |

| PSON | Plastic Small-Outline No-Lead Package | - |

| QSOP | Quarter-Size Small-Outline Package | The pin spacing are width of 0.635 mm.[3] |

| SOIC | Small Outline Integrated Circuit | Also known as SOIC NARROW and SOIC WIDE |

| SSOP | Shrink Small-Outline Package [3] | - |

| TSOP | Thin Small-Outline Package [3] | Example |

| TSSOP | Thin Shrink Small Outline Package [3] | - |

| TVSOP | Thin Very Small-Outline Package [3] | - |

| µMAX | - | Similar to a SOIC. (A Maxim trademark example) |

| WSON | Very Very Thin Small Outline No Lead Package | - |

Chip-Scale packages

Example WL-CSP devices sitting on the face of a

U.S. penny. A

SOT-23 device is shown for comparison.

| Acronym | Full name | Remark |

| CSP | Chip Scale Package | Package size is no more than 1.2× the size of the silicon chip [16][17] |

| TCSP | True Chip Size Package | Package is same size as silicon [18] |

| TDSP | True Die Size Package | Same as TCSP [18] |

| MICRO SMD | - | Chip-size package (CSP) developed by National Semiconductor [19] |

| COB | Chip-on-board | Bare silicon chip, that is usually an integrated circuit, is supplied without a package. |

| COF | Chip-on-flex | Variation of COB, where a chip is mounted directly to a flex circuit. |

| COG | Chip-on-glass | Variation of COB, where a chip is mounted directly to a piece of glass - typically an LCD. |

Ball grid array

Ball Grid Array BGA uses the underside of the package to place pads with balls of solder in grid pattern as connections to PCB.[1][3]

| Acronym | Full name | Remark |

| FBGA | Fine Pitch Ball Grid Array | a square or rectangular array of solder balls on one surface [3] |

| LBGA | Low Profile Ball Grid Array | also known as Laminate Ball Grid Array [3] |

| TEPBGA | Thermally Enhanced Plastic Ball Grid Array | - |

| CBGA | Ceramic Ball Grid Array [3] | - |

| OBGA | Organic Ball Grid Array [3] | - |

| TFBGA | Thin Fine Pitch Ball Grid Array [3] | - |

| PBGA | Plastic Ball Grid Array [3] | - |

| MAP-BGA | Mold Array Process - Ball Grid Array | - |

| UCSP | Micro (μ) Chip Scale Package | similar to a BGA (A Maxim trademark example) [17] |

| μBGA | Micro-Ball Grid Array | with ball spacing less than 1 mm |

| LFBGA | Low Profile Fine Pitch Ball Grid Array [3] | - |

| TBGA | Thin Ball Grid Array [3] | - |

| SBGA | Super Ball Grid Array [3] | above 500 Pin count |

| UFBGA | Ultra Fine Ball Grid Aarray [3] | example |

Transistor, diode, small pin count IC packages

- MELF: Metal Electrode Leadless Face (usually for resistors and diodes)

- SOD: Small Outline Diode.

- SOT: Small-outline transistor (also SOT-23, SOT-223, SOT-323).

- TO-XX: wide range of small pin count packages often used for discrete parts like transistors or diodes.

- TO-3

- TO-5

- TO-18: metal can package with radial leads

- TO-39

- TO-46

- TO-92: plastic encapsulated package with three leads

- TO-99

- TO-100

- TO-126: plastic encapsulated package with three leads and a hole for mounting on a heat sink

- TO-220: through-hole plastic package with a (usually) metal heat sink tab and three leads

- TO-226 [20]

- TO-247 [21]

- TO-252 (also called SOT428, DPAK)[22]

- TO-263, also called D2PAK: SMT package similar to the TO-220

- TO-263 THIN

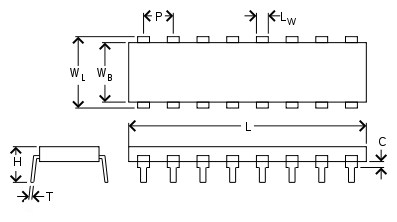

Dimension reference

Surface-mount

C - Clearance between IC body and PCB

H - Total Height

T - Lead Thickness

L - Total Carrier Length

LW - Lead Width

LL - Lead Length

P - Pitch

Through hole

C - Clearance between IC body and board

H Total Height

T - Lead Thickness

L - Total Carrier Length

LW - Lead Width

LL - Lead Length

P - Pitch

WB - IC Body Width

WL - Lead-to-Lead Width-

Package dimensions

All measurements below are given in mm. To convert mm to mils, divide mm by 0.0254 (i.e., 2.54 mm / 0.0254 = 100 mil).

- C - Clearance between package body and PCB.

- H - Height of package from pin tip to top of package.

- T - Thickness of pin.

- L - Length of package body only.

- LW - Pin width.

- LL - Pin length from package to pin tip.

- P - Pin pitch (distance between conductors to the PCB).

- WB - Width of the package body only.

- WL - Length from pin tip to pin tip on the opposite side.

Dual row

| Image | Family | Pin | Name | Package | WB | WL | H | C | L | P | LL | T | LW |

| DIP | Y | Dual Inline Package | 8-DIP | 6.2-6.48 | 7.62 | 7.7 | | 9.2-9.8 | 2.54 (1/10 inch) | 3.05-3.6 | | 1.14-1.73 |

| 32-DIP | | 15.24 | | | | 2.54 (1/10 inch) | | | |

| | LFCSP | N | Lead Frame Chip Scale Package | | | | | | | 0.5 | | | |

| MSOP | Y | Mini Small Outline Package |

8-MSOP | 3 | 4.9 | 1.1 | 0.10 | 3 | 0.65 | 0.95 | 0.18 | 0.17 - 0.27 |

| 10-MSOP | 3 | 4.9 | 1.1 | 0.10 | 3 | 0.5 | 0.95 | 0.18 | 0.17 - 0.27 |

| 16-MSOP | 3 | 4.9 | 1.1 | 0.10 | 4.04 | 0.5 | 0.95 | 0.18 | 0.17 - 0.27 |

| SO

SOIC

SOP | Y | Small Outline Integrated Circuit | 8-SOIC | 3.9 | 5.8-6.2 | 1.72 | 0.10-0.25 | 4.8-5.0 | 1.27 | 1.05 | 0.19-0.25 | 0.39-0.46 |

| 14-SOIC | 3.9 | 5.8-6.2 | 1.72 | 0.10-0.25 | 8.55-8.75 | 1.27 | 1.05 | 0.19-0.25 | 0.39-0.46 |

| 16-SOIC | 3.9 | 5.8-6.2 | 1.72 | 0.10-0.25 | 9.9-10 | 1.27 | 1.05 | 0.19-0.25 | 0.39-0.46 |

| 16-SOIC | 7.5 | 10.00-10.65 | 2.65 | 0.10-0.30 | 10.1-10.5 | 1.27 | 1.4 | 0.23-0.32 | 0.38-0.40 |

| SOT | Y | Small Outline Transistor | SOT-23-8 | 1.6 | 2.8 | 1.45 | | 2.9 | 0.95 | 0.6 | | 0.22-0.38 |

| | SSOP | Y | Shrink Small-Outline Package | | | | | | | | | | |

| | TDFN | N | Thin Dual Flat No-lead | 8-TDFN | 3 | 3 | 0.7-0.8 | | 3 | 0.65 | N/A | | 0.19-0.3 |

| | TSOP | Y | Thin Small-Outline Package | | | | | | | | | | |

| TSSOP | Y | Thin Shrink Small Outline Package | 8-TSSOP | 4.4 | 6.4 | 1.2 | 0.15 | 3 | 0.65 | | 0.09-0.2 | 0.19-0.3 |

| | µSOP | Y | Micro Small Outline Package[23] | µSOP-8 | | 4.9 | 1.1 | | 3 | 0.65 | | | |

| | US8[24] | Y | US8 Package | | 2.3 | 3.1 | .7 | | 2 | .5 | | | |

Quad rows

| Image | Family | Pin | Name | Package | WB | WL | H | C | L | P | LL | T | LW |

| PLCC | N | Plastic Leaded Chip Carrier | | | | | | | 1.27 | | | |

| | CLCC | N | Ceramic Leadless Chip Carrier | 48-CLCC | 14.22 | 14.22 | 2.21 | | 14.22 | 1.016 | N/A | | 0.508 |

| LQFP | Y | Low-profile Quad Flat Package | | | | | | | 0.50 | | | |

|

| TQFP | Y | Thin Quad Flat Package | TQFP-44 | 10.00 | 12.00 | | 0.35-0.50 | | 0.80 | 1.00 | 0.09-0.20 | 0.30-0.45 |

| | TQFN | N | Thin Quad Flat No-lead | | | | | | | | | | |

LGA

| Package | x | y | z |

| 52-ULGA | 12mm | 17mm | .65mm |

| 52-ULGA | 14mm | 18mm | .10mm |

| 52-VELGA | ? | ? | ? |

See also

Multi-chip packages

Occasionally people put several chips of silicon in a single package.

A variety of techniques for interconnecting several chips within a single package have been proposed and researched:

See also

References

- 1 2 3 4 5 6 7 8 9 10 11 12 13 14 "CPU Collection Museum - Chip Package Information". The CPU Shack. Retrieved 2011-12-15.

- ↑ http://www.national.com/ms/PA/PACKING_CONSIDERATIONS__METHODS__MATERIALS_AND_REC.pdf

- 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 "Integrated Circuit, IC Package Types; SOIC. Surface Mount Device Package". Interfacebus.com. Retrieved 2011-12-15.

- ↑ "National Semiconductor CERPACK Package Products". National.com. Retrieved 2011-12-15.

- ↑ "National Semiconductor CQGP Package Products". National.com. Retrieved 2011-12-15.

- ↑ "National's LLP Package". National.com. Retrieved 2011-12-15.

- ↑ "LTCC Low Temperature Co-fired Ceramic". Minicaps.com. Retrieved 2011-12-15.

- ↑ "IEEE Xplore - Performance evaluation of MCM chip-to-chip interconnections using custom I/O buffer designs". Ieeexplore.ieee.org. doi:10.1109/ASIC.1993.410760. Retrieved 2011-12-15.

- ↑ "National Semiconductor Launches New Generation of Ultra-Miniature, High Pin-Count Integrated Circuit Packages". National.com. Retrieved 2011-12-15.

- ↑ Meyers, Michael; Jernigan, Scott (2004). Mike Meyers' A+ Guide to PC Hardware. The McGraw-Hill Companies. ISBN 978-0-07-223119-9.

- ↑ Archived August 18, 2011, at the Wayback Machine.

- ↑ "Press Releases - Motorola Mobility, Inc". Motorola.com. Retrieved 2011-12-15.

- ↑ "Xilinx new CPLDs with two I/O banks". Eetasia.com. 2004-12-08. Retrieved 2011-12-15.

- ↑ "Packages". Chelseatech.com. 2010-11-15. Retrieved 2011-12-15.

- ↑ http://cpu.linuxmania.net/liste/cpuinfo/chip-package/SIDEBRAZE_DIP/chip-package-sidebraze.htm

- ↑ "CSP - Chip Scale Package". Siliconfareast.com. Retrieved 2011-12-15.

- 1 2 "Understanding Flip-Chip and Chip-Scale Package Technologies and Their Applications - Maxim". Maxim-ic.com. 2007-04-18. Retrieved 2011-12-15.

- 1 2 "Chip Scale Review Online". Chipscalereview.com. Retrieved 2011-12-15.

- ↑ "Packaging Technology | National Semiconductor – Package Drawings, Part Marking, Package Codes, LLP, micro SMD, Micro-Array". National.com. Retrieved 2011-12-15.

- ↑ http://www.siliconfareast.com/to226.htm

- ↑ http://www.vishay.com/docs/95223/to247.pdf

- ↑ NXP.

"SOT428".

- ↑ http://pdfserv.maximintegrated.com/package_dwgs/21-0036.PDF

- ↑ "Fairchild's TinyLogic family overview" (PDF). March 22, 2013.

- ↑ Proximity Communication - the Technology, 2004, archived from the original on 2009-07-18

External links

|

|---|

|

| Diode |

- DO-204 (DO-35 / DO-41)

- DO-213 (MELF)

- DO-214 (SMA / SMB / SMC)

- SOD (SOD-123 / SOD-323 / SOD-523 / SOD-923)

|

|---|

|

| Transistor | |

|---|

|

| Single row | |

|---|

|

| Dual row | |

|---|

|

| Quad row | |

|---|

|

| Grid array | |

|---|

|

| Wafer | |

|---|

|

| Related topics | |

|---|

|

Note: It's relatively common to find packages that contain other components than their designated ones, such as diodes or voltage regulators in transistor packages, etc. |

.svg.png)